1. Kondisi [Kembali]

Modul 1 Percobaan 1 Kondisi 7

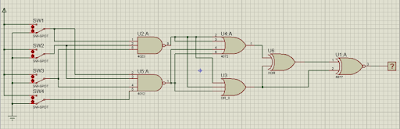

Buatlah sebuah rangkaian lengkap yang memuat 2

gerbang NAND dengan 3 input dan 4 input, kemudian gerbang OR dengan 3 dan 4

input,kemudian 1 gerbang XOR dan 1 gerbang XNOR. Dan output akhir rangkaian

keseluruhannya ditunjukkan dengan LED atau LOGIC PROBE. Dimana input awal

berupa 4 saklar SPDT.

2. Gambar Rangkaian Simulasi [Kembali]

Rangkaian Sebelum disimulasikan :

3. Video Simulasi [Kembali]

4. Prinsip Kerja [Kembali]

Pada rangakaian di atas input awal adalah 4 buah saklar SPDT yang mana kaki positif dihubungkan ke Vcc sumber dan kaki negatif terhubung ke ground. Terdapat 2 buah gerbang NAND 3 input dan 4 input, dimana masing-masing kaki gerbang terhubung ke saklar sesuai urutan, kaki 1 gerbang NAND terhubung ke saklar 1, kaki 2 gerbang NAND terhubung ke saklar 2, kaki 3 gerbang NAND terhubung ke saklar 3, dan untuk kaki 4 gerbang NAND 4 input terhubung ke saklar 4. Terdapat 2 Gerbang logika OR dengan 3 input dan 4 input, kemudian terdapat 1 XOR dan 1 XNOR. Keluaran dari gerbang logika sesuai dengan nilai tabel kebenaran masing masing gerbang dan sesuai dengan letak saklarnya sehingga didapatkan keluaran akhir rangkaian bernilai 1 atau 0.

Jadi pada rangkaian di atas kita lakukan percobaan dengan empat saklar berlogika 1:1:1:1 maka input pada NAND gate 3 input yaitu berlogika 1:1:1 sehingga menghasilkan output 0 dan pada input pada NAND gate 4 input yaitu berlogika 1:1:1:1 sehingga menghasilkan output 0.

Sesuai dengan table kebenaran dari gerbang NAND yaitu jika inputanya ada yang berlogika 0 maka outputnya akan berlogika 1, jika tidak outputnya akan berlogika 0

Tidak ada komentar:

Posting Komentar