1. Dioda Zener <kembali>

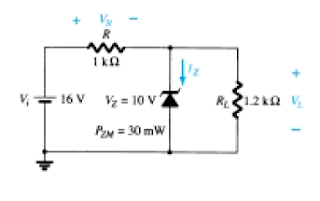

Contoh 2.26

|

| Gambar 2.109 |

(a) Untuk jaringan dioda Zener dari Gambar 2.109, tentukan VL, VR, IZ, dan PZ.

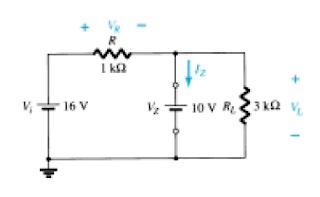

(b) Ulangi bagian (a) dengan RL = 3 k.

Solusi

(a) Mengikuti prosedur yang disarankan jaringan digambar ulang seperti yang ditunjukkan pada Gambar. 2.110. Menerapkan Persamaan. (2.16)

Karena V= 8.73 V kurang dari VZ= 10 V, dioda dalam keadaan "mati" seperti yang ditunjukkan pada karakteristik Gambar. 2.111. Mengganti setara dengan sirkuit terbuka akan menghasilkan dalam jaringan yang sama seperti pada Gambar. 2.110, di mana kami menemukan itu

(b) Menerapkan Persamaan. (2.16) sekarang akan menghasilkan

|

| Gambar 2.112 |

Contoh 2.27

|

| Gambar 2.113 |

(a) Untuk jaringan Gambar 2.113, tentukan kisaran RL dan IL yang akan dihasilkan dalam VRL dipertahankan pada 10 V.

(b) Tentukan peringkat watt maksimum dioda.

Solusi

|

| Gambar 2.114 VL versus RL dan IL untuk regulator Gambar 2.113. |

Contoh 2.28

Tentukan kisaran nilai Vi yang akan mempertahankan dioda Zener dari Gambar 2.115 dalam "on" state.

|

| Gambar 2.115 Regulator untuk Contoh 2.28. |

Solusi

|

Gambar 2.116 Plot VL versus Vi untuk pengatur Gambar 2.115.

|

2. Combination Network <kembali>

Contoh 6.13

|

| Gambar 6.45 |

Tentukan tingkat VD dan VC untuk jaringan Gambar. 6.45.

Solusi

Dari pengalaman masa lalu kita sekarang menyadari bahwa VGS biasanya merupakan jumlah yang penting menentukan atau menulis persamaan ketika menganalisis jaringan JFET. Karena VGS adalah a tingkat di mana solusi langsung tidak jelas, mari kita mengalihkan perhatian kita ke konfigurasi transistor. Konfigurasi pembagi tegangan adalah salah satu tempat perkiraan teknik dapat diterapkan (βRE= (180 X 1,6 kΩ)= 288 kΩ > 10R2 240 kΩ), memungkinkan penentuan VB menggunakan aturan pembagi tegangan pada sirkuit input.

Pertanyaan tentang bagaimana menentukan VC tidak begitu jelas. Baik VCE dan VDS tidak diketahui jumlah yang mencegah kami membuat tautan antara VD dan VC atau dari VE ke VD. Pemeriksaan yang lebih hati-hati dari Gambar 6.45 mengungkapkan bahwa VC terkait dengan VB oleh VGS (dengan asumsi VRG 0 V). Karena kita tahu VB jika kita dapat menemukan VGS, VC bisa ditentukan dari

Pertanyaan kemudian muncul bagaimana menemukan tingkat VGSQ dari diam nilai ID. Keduanya terkait oleh persamaan Shockley:

dan VGSQ dapat ditemukan secara matematis dengan memecahkan VGSQ dan mengganti numerik nilai-nilai. Namun, mari kita beralih ke pendekatan grafis dan cukup bekerja di urutan terbalik digunakan pada bagian sebelumnya. Karakteristik transfer JFET pertama kali dibuat sketsa seperti yang ditunjukkan pada Gambar. 6.46. Tingkat IDQ kemudian ditetapkan secara horizontal baris seperti yang ditunjukkan pada gambar yang sama. VGSQ kemudian ditentukan dengan menjatuhkan garis turun dari titik operasi ke sumbu horizontal, menghasilkan

aa

Tingkat VC:

|

Gambar 6.46 Menentukan Q-point untuk jaringan Fig. 6.45

|

Contoh 6.14

|

| Gambar 6.47 |

Tentukan VD untuk jaringan Gambar 6.47.

Solusi

Dalam hal ini, tidak ada jalur yang jelas untuk menentukan level tegangan atau arus untuk konfigurasi transistor. Namun, beralih ke JFET yang bias sendiri, persamaan untuk VGS dapat diturunkan dan titik diam yang dihasilkan ditentukan menggunakan grafik teknik. Itu adalah,

menghasilkan garis bias diri yang muncul pada Gambar 6.48 yang membentuk diam menunjuk pada

Untuk transistor

|

| Gambar 6.48 Menentukan Q-point untuk jaringan Fig. 6.47. |

3. JFET Common-Gate Configuration <kembali>

Contoh 9.10

|

| Gambar 9.32 |

Meskipun jaringan Gambar 9.32 awalnya mungkin tidak tampak dari gerbang umum variasi, pemeriksaan dekat akan mengungkapkan bahwa ia memiliki semua karakteristik Gambar. 9.29. Jika VGSQ= -2.2 V dan IDQ 2.03 mA:

(a) Tentukan gm.

(b) Temukan rd.

(c) Hitung Zi dengan dan tanpa rd. Bandingkan hasil.

(d) Temukan Zo dengan dan tanpa rd. Bandingkan hasil.

(e) Tentukan Vo dengan dan tanpa rd. Bandingkan hasil.

Solusi

4. High Frequency Response-FET Amplifier <kembali>

Contoh 11.12

(a) Tentukan frekuensi cutoff tinggi untuk jaringan Gambar 11.52 menggunakan parameter yang sama dengan Contoh 11.10:

(b) Tinjau respons PROBE untuk rentang frekuensi penuh dan catat apakah itu mendukung kesimpulan dari Contoh 11.10 dan perhitungan di atas.

Solusi

Hasil di atas dengan jelas menunjukkan bahwa kapasitansi input dengan kapasitansi efek Miller akan menentukan frekuensi cutoff atas. Ini biasanya terjadi karena nilai Cds yang lebih kecil dan level resistensi yang ditemui di sirkuit output.

(b) Menggunakan PSpice Windows, skema untuk jaringan akan muncul seperti yang ditunjukkan pada Gbr. 11.55.

|

| Gambar 11.55 Jaringan Gambar 11.52 dengan nilai yang ditetapkan. |

Tidak ada komentar:

Posting Komentar